# SPARCserver 1000 POST User's Guide

Sun Microsystems Computer Corporation 2550 Garcia Avenue Mountain View, CA 94043 U.S.A.

Part No: 801-2916-10 Revision A, May 1993 © 1993 Sun Microsystems, Inc.

2550 Garcia Avenue, Mountain View, California 94043-1100 U.S.A.

All rights reserved. This product and related documentation are protected by copyright and distributed under licenses restricting its use, copying, distribution, and decompilation. No part of this product or related documentation may be reproduced in any form by any means without prior written authorization of Sun and its licensors, if any.

Portions of this product may be derived from the UNIX® and Berkeley 4.3 BSD systems, licensed from UNIX System Laboratories, Inc. and the University of California, respectively. Third-party font software in this product is protected by copyright and licensed from Sun's Font Suppliers.

RESTRICTED RIGHTS LEGEND: Use, duplication, or disclosure by the United States Government is subject to the restrictions set forth in DFARS 252.227-7013 (c)(1)(ii) and FAR 52.227-19.

The product described in this manual may be protected by one or more U.S. patents, foreign patents, or pending applications.

#### **TRADEMARKS**

Sun, Sun Microsystems, Sun Microsystems Computer Corporation, the Sun logo, the SMCC logo, are trademarks or registered trademarks of Sun Microsystems, Inc. UNIX and OPEN LOOK are registered trademarks of UNIX System Laboratories, Inc.. All other product names mentioned herein are the trademarks of their respective owners.

All SPARC trademarks, including the SCD Compliant Logo, are trademarks or registered trademarks of SPARC International, Inc. SPARCstation, SPARCserver, SPARCengine, SPARCworks, and SPARCompiler are licensed exclusively to Sun Microsystems, Inc. Products bearing SPARC trademarks are based upon an architecture developed by Sun Microsystems, Inc.

The OPEN LOOK® and Sun™ Graphical User Interfaces were developed by Sun Microsystems, Inc. for its users and licensees. Sun acknowledges the pioneering efforts of Xerox in researching and developing the concept of visual or graphical user interfaces for the computer industry. Sun holds a non-exclusive license from Xerox to the Xerox Graphical User Interface, which license also covers Sun's licensees who implement OPEN LOOK GUIs and otherwise comply with Sun's written license agreements.

X Window System is a trademark and product of the Massachusetts Institute of Technology.

THIS PUBLICATION IS PROVIDED "AS IS" WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT.

THIS PUBLICATION COULD INCLUDE TECHNICAL INACCURACIES OR TYPOGRAPHICAL ERRORS. CHANGES ARE PERIODICALLY ADDED TO THE INFORMATION HEREIN; THESE CHANGES WILL BE INCORPORATED IN NEW EDITIONS OF THE PUBLICATION. SUN MICROSYSTEMS, INC. MAY MAKE IMPROVEMENTS AND/OR CHANGES IN THE PRODUCT(S) AND/OR THE PROGRAM(S) DESCRIBED IN THIS PUBLICATION AT ANY TIME.

# **Contents**

|    | Preface                     | vii  |

|----|-----------------------------|------|

| 1. | Overview of POST            | 1-1  |

|    | 1.1 Features of POST        | 1-1  |

|    | 1.2 Invoking POST           | 1-2  |

|    | 1.2.1 System and Board LEDs | 1-3  |

|    | 1.2.2 Error Messages        | 1-4  |

|    | 1.3 User Interface Commands | 1-6  |

|    | 1.4 DEMON Menu Options      | 1-8  |

| 2. | Test Descriptions           | 2-1  |

|    | 2.1 Early POST Tests        | 2-2  |

|    | 2.2 Board Level Testing     | 2-3  |

|    | 2.3 Loopback Exit           | 2-81 |

|    | 2.4 System Master Selection |      |

|    | 2.5 System Level Testing    |      |

|    | 2.6 System Reconfiguration  |      |

| A. | Sample POST Output                 | <b>A</b> -1 |

|----|------------------------------------|-------------|

| В. | POST Design Concepts               | <b>B</b> -1 |

|    | B.1 Tests and Subtests             | B-1         |

|    | B.1.1 TestIDs and SubtestIDs       | B-1         |

|    | B.1.2 TestLists and Sequencers     | B-2         |

|    | B.1.3 Test Levels and Error Levels | B-2         |

|    | B.1.4 Test Design                  | B-2         |

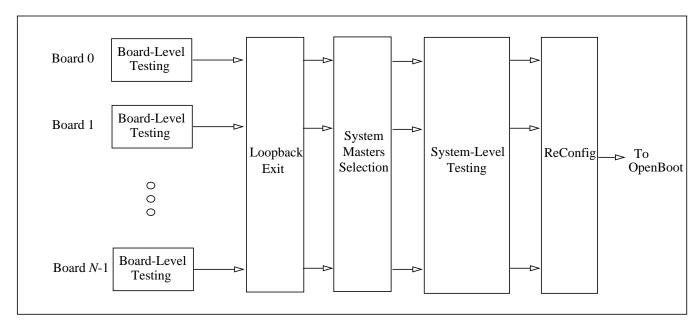

|    | B.2 Phases of POST                 | B-3         |

|    | B.3 Error Handling                 | B-5         |

|    | B.4 Running POST                   | В-6         |

|    | Glossary Glossa                    | ry-1        |

|    | Index Ind                          | ex-1        |

# **Tables**

| Table P-1 | Typographic Conventions     | viii |

|-----------|-----------------------------|------|

| Table P-2 | Related Documentation       | ix   |

| Table 1-1 | Error Message Fields        | 1-4  |

| Table 1-2 | User Interface Key Commands | 1-6  |

## Preface

This manual, *SPARCserver*<sup>TM</sup> 1000 POST User's Guide, describes the Power-On Self-Test (POST) software that is part of the diagnostics that test the SPARCserver 1000 system. POST resides in the boot PROM (programmable read-only memory) on each SPARCserver 1000 system board.

The information in this manual is for manufacturing and test engineers, repair depot and field service personnel, and diagnostics engineers who test the SPARCserver 1000 system. The manual does not describe the system architecture; it assumes you are familiar with such hardware concepts. It provides some background information about the POST software, explains how you can use it, and contains detailed information about the tests that make up the software.

The manual is organized as follows:

### **Chapter 1: Overview of POST**

The first chapter introduces you to POST and tells you how to use the software.

### **Chapter 2: Test Descriptions**

The second chapter comprehensively describes the tests of the POST software. For each test, there is a test description, an LED pattern, the basic steps executed by the test, and a summary of error messages.

### **Appendix A: Sample POST Output**

This appendix shows the results of a sample run of the POST software.

#### **Appendix B: POST Design Concepts**

This appendix describes the design principles for POST.

### Glossary

The glossary enhances your understanding of POST by defining the SPARCserver 1000 system terminology.

## Typographic Changes and Symbols

The following table describes the font and symbol conventions used in this manual.

Table P-1 Typographic Conventions

| Typeface or<br>Symbol | Meaning                                                                                                                       | Example                                                                                                            |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| AaBbCc123             | The names of commands, files, and directories; on-screen computer output                                                      | Edit your .login file.<br>Use ls -a to list all files.<br>system% You have mail.                                   |

| AaBbCc123             | What you type, contrasted with<br>on-screen computer output;<br>Also, the POST test names will<br>be shown with this typeface | system% <b>su</b><br>Password:                                                                                     |

| AaBbCc123             | Command-line placeholder: replace with a real name or value                                                                   | To delete a file, type rm filename.                                                                                |

| AaBbCc123             | Book titles, new words or terms, or words to be emphasized                                                                    | Read Chapter 6 in <i>User's Guide</i> . These are called <i>class</i> options. You <i>must</i> be root to do this. |

## Related Manuals

For more information on the SPARCserver 1000 system, refer to the documents listed below.

Table P-2 Related Documentation

| Category     | Manual Title                                                                                   | Part Number      |

|--------------|------------------------------------------------------------------------------------------------|------------------|

| Installation | Memory Module Installation Guide                                                               | 801-2 <i>030</i> |

|              | SPARCserver 1000 Installation Manual                                                           | 800-2893         |

|              | SPARCserver 1000 System Board Manual                                                           | 800-2900         |

| Diagnostics  | OpenBoot Command Reference                                                                     | 800-6076         |

| Service      | SPARCserver 1000 Service Manual                                                                | 801-2895         |

| Safety       | Sun SPARCserver 1000 Cabinet and Data Center Expansion Cabinet<br>Regulatory Compliance Manual | 801-2892         |

Prefacee

The SPARCserver 1000 system's Power-On Self-Test (POST) software automatically tests the hardware resources of the system at power up or reset. POST resides in the boot PROM (programmable read-only memory) on each processor board in a SPARCserver 1000 system. It runs as a stand-alone diagnostic and multiprocessor control program.

### 1.1 Features of POST

The SPARCserver 1000 POST has a functionality far greater than any Sun™ system POST so far. Based on test results and on customer-defined resource preferences, POST selects the optimal system configuration using as many working resources as possible. It thus tries to provide a reliable machine configuration that can be used by the OpenBoot™ firmware.

### POST has two goals:

- Offer the customer a wide platform for applications even if there are hardware failures

- Facilitate field replacement and factory repair.

To these ends, it records error history information about failed or marginally functional components and also provides field replaceable unit (FRU)-level diagnostic information. A detailed log, containing information about which tests have passed and which have failed, is available after each POST run. The FRU-level information is useful for both manufacturing and field service

personnel to determine functional components. The more detailed information, which is recorded from relevant hardware error registers each time there is a failure, helps fault diagnosis in the factory.

The most important new feature of POST, which differentiates it from POST in earlier Sun machines, is *automatic reconfiguration*. When POST finds hardware failures, it tries to reconfigure the system optimally, using as many functional I/O components as possible.

## 1.2 Invoking POST

Before you begin running POST, make sure you have a SPARCserver 1000 system with a serial cable running from the system board in the lowest numbered slot to a TTY terminal or equivalent. You need this set up to see status and error information during POST execution.

You can invoke POST in one of these ways:

- Turn on the power to your SPARCserver 1000 system.

- Press the system reset switch, which is located under the front panel.

Depending on the position of the key switch (which is on the front of the system, under the front panel), POST will execute in *normal mode* (key switch in the normal or SECURE position) or diagnostic mode (key switch in the DIAG position). (Diagnostic mode is hereafter called *diag mode*.)

#### Normal Mode

Normal mode is used for booting the operating system quickly. In normal mode, the actual operation of POST is transparent to the user. POST initializes the SPARCserver 1000 hardware state and tests all system board components out to the SBus connectors. If errors are detected, POST attempts to recover by modifying the system configuration to exclude the faulty components. When POST completes, it transfers control to the OpenBoot firmware, which then boots the operating system. In normal mode, POST should transfer control to OpenBoot firmware within one minute; it does not display any status messages, but it does display error messages as they occur.

#### Diag Mode

Diag mode is used to test and troubleshoot the SPARCserver 1000 system boards. In diag mode, POST executes a larger set of diagnostics, which provide additional coverage and better isolation of failing components on the system boards. In diag mode, you can communicate with POST. You can control POST using keyboard commands and you can use its test control features. POST is very verbose in this mode. (See Appendix A for a sample POST run.)

## 1.2.1 System and Board LEDs

The SPARCserver 1000 system has three system LEDs and ten board LEDs. Their function is described in this section.

#### System LEDs

The left system LED is green, the center LED is yellow, and the right LED is green

- The left LED (green) is the power indicator. Once the power to the system is turned on, this LED always remains lit (ON).

- When the center LED (yellow) is ON, it indicates that POST is running.

- If the center LED (yellow) remains lit for more than 1 minute in normal mode, and the right LED (green) never lights up, it shows that the machine is unable to boot. (In diag mode this LED remains lit for longer than one minute.)

- If the center and right LEDs light up simultaneously, it shows that the system has booted with failing components, which POST has disabled. (You should be able to boot UNIX or other stand-alone diagnostics.)

- If the right LED (green) is ON and the center LED (yellow) is OFF, it indicates that the system has passed POST without any failures.

#### **Board LEDs**

The ten board LEDs work as follows:

- Two green board LEDs (A and B) indicate the presence of functional processors on a board at end of a POST run.

- The eight yellow LEDs

- Output test ID numbers during a POST run

- Indicate boards with failed parts at end of POST

- Are always lit on non-processor boards.

- The Boot Master constantly runs a Walking 1s pattern on the yellow LEDs.

## 1.2.2 Error Messages

In both normal and diag modes, error messages are sent to the TTY port and are displayed on any terminal that is connected to that port. The ID of the failing test is also displayed in the eight LEDs on the edge of the system board. (See Chapter 2, "Test Descriptions" for test LED patterns.)

The general format for a POST error message is as follows:

```

bp> TEST STATUS - test_name.subtest_name ID LED

bp> Description of Error

Address = 0x%X

Data = 0x%X

```

Table 1-1 explains what each field in the error message means.

Table 1-1 Error Message Fields

| Field        | Description                                  |

|--------------|----------------------------------------------|

| b            | System board number.                         |

| p            | Processor (A or B).                          |

| TEST_STATUS  | Status of the test (pass or fail).           |

| test_name    | Name of the test.                            |

| subtest_name | Name of the subtest.                         |

| ID           | Unique test and subtest id number.           |

| LED          | Value (hex) of the LED display for the test. |

Error messages also show a line explaining the failure, and display information from relevant registers.

Samples of error messages displayed by POST are shown below. The first example shows that the test BWO Regs has failed because its subtest (Timers and Interrupts) has failed. The test ID is 38.3, and the LED pattern for the test is 0x26.

The example below shows the failing test and subtest (CO SBI and SBI Registers). The test ID is 56.1 and the LED pattern for this test is 0x36.

```

0A> TEST FAILED - C0 SBI.SBI Registers ID 56.1 LED 0x38

0A> While testing Component ID register an unexpected trap occurred

MFSR = 00000936

MFAR = 02800000

Trap Type = 9

CC Error = 00000000.F01E1D58

```

## 1.3 User Interface Commands

In diag mode you can interact with POST in a limited way, using the commands shown in Table 1-2.

Table 1-2 User Interface Key Commands

| Key    | Action                                                                                                                                                                                                                     |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| a      | Toggle Pause CPU A flag. Press this key to stall selftest on CPU A. Press any key to resume selftest. (Affects both CPUs. POST freezes on current system board; other system boards continue.)                             |

| b      | Toggle Pause CPU B flag. Press this key to stall selftest on CPU B. Press any key to resume selftest. (Affects both CPUs. POST freezes on current system board; other system boards continue.)                             |

| C      | Toggle Trace Test Case flag. Set this flag to allow subtests to display trace messages on the console. This is helpful for debugging or troubleshooting the system.                                                        |

| е      | Toggle Loop On Error flag. Set this flag, and the current test will loop on an error till the flag is reset. If the flag is not set, the current test will try and continue execution once an error occurs.                |

| h or ? | Use either key to display this command summary                                                                                                                                                                             |

| 1      | Toggle Loop On Subtest flag.  Press this key to cause the test sequencer to loop on the current subtest.  (Can be an effective scope loop.)                                                                                |

| m      | Go to DEMON menus. Set this flag to interrupt the POST run, call a DEMON, and display the DEMON menu.                                                                                                                      |

| n      | Skip to next subtest.  Set this flag to cause the current subtest to exit and return to the sequencer. The next subtest in the list is then dispatched.  (Useful for skipping long subtests.)                              |

| р      | Toggle Print All Errors flag. Set this flag to allow POST to display all the errors within each test. Reset the flag if only the first error in each test is to be displayed. (Default is to print one error per subtest.) |

Table 1-2 User Interface Key Commands (Continued)

| Key          | Action                                                                                                                                                                                                                                |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| s            | Toggle Stop POST flag. Set this flag to allow POST to stop after it finishes execution and before it transfers control to the OpenBoot firmware. The DEMON menu is displayed.                                                         |

| t            | Toggle Timestamp flag. Set this flag to allow the sequencer to print a timestamp prior to dispatching each subtest. (Uses TOD clock.)                                                                                                 |

| v            | Toggle Verbose Print Mode flag. Set this flag to allow POST to display the name of each step as it goes through the system initialization sequence. Reset the flag, and POST displays only the major milestones and the spin loopbar. |

| N            | Skip to next test. Set this flag to terminate the current test list and allow the sequencer to fetch the next test list.                                                                                                              |

| spaceba<br>r | Skip to next test case.  Set this flag while a subtest is looping on error and the loop will exit and the subtest will continue by breaking out of the current loop. (Useful when looping on error.)                                  |

## 1.4 DEMON Menu Options

The DEMON options are useful when troubleshooting the system; they are not required in a normal POST run. To use the DEMON menus, type  ${\tt m}$  (see Table 1-2) to interrupt POST while it is running in diag mode.

The DEMON main menu is shown below.

```

DEMON

1A>Select one of the following functions

1A> '0' System Parameters

1A> '1' Read/Write device

1A> '2' Software Reset

1A> '3' NVRAM Management

1A> '4' Error Reporting

1A> '5' Analyze Error Logs

1A> '6' Power Off at Main Breaker

1A> '7' NVRAM SIMM tests

1A> 'r' Return to selftest

1A>

Command ==>

```

To go to another menu or to select a command from this menu, type the number or letter that corresponds to the option (all other keys are ignored).

## System Parameters Option

Type 0 at the main menu prompt, to get to the System Parameters submenu.

This sub-menu has several useful features for debugging and troubleshooting POST problems. You can view system reports, check component IDs, clear error logs, and dump system board registers.

#### Read/Write Device Option

Type 1 at the main menu prompt, to get to the Read/Write device submenu.

This sub-menu allows you to read and write using ASIs (address space identifiers). Most of the SPARCserver 1000 ASICs can be accessed in this way. To use this menu, you must have detailed knowledge of how system physical addresses are assigned to the ASICs.

#### Software Reset Option

The Software Reset DEMON option does not have a menu. When you type 2 at the main menu prompt, POST issues a software reset to the BootBus reset register. The system is reset, and POST returns to the DEMON menu.

#### **NVRAM Management Option**

Type 3 at the main menu prompt, to get to the NVRAM Management sub-menu.

This sub-menu is used to manage the memory SIMM test results in BootBus NVRAM. It allows you to view and erase the data.

### Error Reporting Option

Type 4 at the main menu prompt, to get to the Error Reporting sub-menu.

This sub-menu is used to print out data saved on the last system watchdog reset. The sub-menu does not allow you to dump data from boards that are not present. If the menu is not used at end of POST, only data from the local board can be dumped. (The "data" is the unformatted contents of all JTAG-scannable ASIC registers.)

### Analyze Error Logs Option

The Analyze Error Logs DEMON option does not have a menu. When you type 5 at the main menu prompt, POST begins analyzing and displaying the error logs.

POST always logs the last System Watchdog error in BootBus NVRAM. The Analyze Error Logs option analyzes System Watchdog error logs. If there are any error bits set, POST formats and displays the relevant data.

This function is also be invoked by:

- All board masters upon a System Watchdog Reset. In this case, each board

can only see its own error log because the BICs are in loopback.

(Note that the POST System Master maintains and analyzes the error log for

all non-processor boards.)

- The POST System Master after the loopback exit phase of testing (only if there was a recent System Watchdog). In this case, the POST System Master analyzes the error log from each board in the system. If no error bits are set, you only see a banner for that board.

Note – For troubleshooting purposes only, it is possible to clear the error logs using the DEMON menus. The timestamp for each error log is taken from the TOD on that board. If the operating system has not initialized the TOD, ignore the timestamp and use the Clear Error Logs option from the System Parameters menu for this task.

#### Power Off at Main Breaker Option

The Power Off at Main Breaker DEMON option does not have a menu. When you type 6 at the main menu prompt, POST trips the main breaker (this is for manufacturing tests only).

### NVRAM SIMM Tests Option

Type 7 at the main menu prompt, to get to the NVRAM SIMM tests sub-menu.

This option is provided for users to test the NVRAM SIMMs. The operating system uses NVRAM SIMMs to store data. POST never writes to NVRAM SIMMs; it only checks the batteries.

**Note** – Never run these tests on a system that is operational, since vital operating system data might be erased.

### Return To Selftest Option

Type  $\mathbf{r}$  to leave the DEMON menus. You are taken back to the point where you interrupted POST execution when you called the DEMON, and the test execution continues.

The following screens are an example of how you can use various options in the DEMON menus. The example begins with the selection of option 0, System Parameters from the DEMON main menu.

```

0A>

DEMON

OA>Select one of the following functions

0A>

`O'

System Parameters

111

0A>

Read/Write device

121

0A>

Software Reset

0A>

131

NVRAM Management

۱4′

0A>

Error Reporting

۱5′

0A>

Analyze Error Logs

۱6′

0A>

Power Off at Main Breaker

۱7′

0A>

NVRAM SIMM tests

`r'

Return to selftest

0A>

0A>

Command ==> 0

0A>

System Parameters

OA>Select one of the following functions

0A>

۱0′

Set POST Level

0A>

11'

Dump Device Table

12'

0A>

Display System

131

0A>

Dump Board Registers

۱4′

0A>

Dump Component IDs

0A>

`5'

Clear Error Logs

0A>

۱6′

Display Simms

۱7′

0A>

Scrub Main Memory

0A>

\r'

Return

Command ==> 2

0A>

WARNING Board 2 has failed POST

0A>

(0=failed,1=passed,blank=untested/unavailable)

(sbus 1=card present, 0=card not present, x=failed)

0A>----+---+

0A>Slot|cpuA|bw0|cpuB|bw0|bb|ioc0|sbi|mqh0|mem|sbus|xd0|

1 | 1|

1 | 1 | 1 | 64 | 0001 | 1

| 1 | 1

0A>

1 | 1

1 | 1 | 1

|512|1001| 1

| 1

1 |

0

1 | 1 | 1 | 128 | 0001 | 1

0A>

```

```

0A>Memory Group Status

(0=failed,1=passed,m=simm missing,c=simm mismatch,blank=unpopulated/unused)

0A>+---+

0A>Slot | g0 | g1 | g2 | g3 |

0A>+---+

0A> 0 | 1 | 1 |

0A> 1 |

1 |

1

1 |

0A> 2 | 1 | 1 |

1 | 1 |

0A>+---+

OA>Hit any key to continue :

0A>

System Parameters

OA>Select one of the following functions

` O '

0A>

Set POST Level

11′

0A>

Dump Device Table

0A>

12′

Display System

0A>

131

Dump Board Registers

۱4′

0A>

Dump Component IDs

0A>

`5'

Clear Error Logs

۱6′

0A>

Display Simms

0A>

۱7′

Scrub Main Memory

0A>

`r'

Return

Command ==> 3

0A>Which Board? 0

0A>Probing E0000000

0A>

BW Register Base E0000000

0A>

Comp Id

10D3907D

0A>

DCSR

0001A000.0000DD00

0A>

DDR

FFFFFFFF.FFFFFFF

CTL

0A>

00002000

ITBL

0A>

0A>

0000

0000

0A>

0A>

0000

0A>

0000

0A>

0000

0A>

0000

0A>

0000

0A>

0000

```

```

0A>Probing E0800000

0A>

BW Register Base E0800000

0A>

Comp Id

10D3907D

0A>

DCSR

0001A000.8000DD00

0A>

DDR

0000000.0000000

0A>

CTL

00002020

0A>

ITBL

0000

0A>

0A>

0000

0A>

0000

0A>

0000

0000

0A>

0A>

0000

0A>

0000

0000

0A>

0A>Probing 01F00000

0A> CC Register Base01F00000

0A> StreamData

OA> Stream Data[0] 01F00000 00000000 00000000

0A> Stream Data[1] 01F00008 00000000 00000000

OA> Stream Data[2] 01F00010 00000000 00000000

OA> Stream Data[3] 01F00018 00000000 00000000

OA> Stream Data[4] 01F00020 00000000 00000000

OA> Stream Data[5] 01F00028 00000000 00000000

OA> Stream Data[6] 01F00030 00000000 00000000

OA> Stream Data[7] 01F00038 00000000 00000000

0A> StreamSrcAddr 01F00100 80000010 06000000

0A> StreamDstAddr 01F00200 80000010 0EAABFC0

0A> RefMissCnt

01F00300 00000000 00000000

0A> IntrptPend

01F00406

0A> IntrptMask

01F00506 7FFE

0A> BIST

01F00804 23AA97E6

01F00A04 0000002C

0A> Control

0A> RC=0, DCB=0, WI=0, PF=1, MC=0, PE=1, CE=1, CS_HC=0

0A> Status

01F00B00 0000000F FFF00002

0A> SXP=0, SM=0, NCSID=0, NCSPA=FFFF00 NCSPC=0, SPC=0, BC=0, WP=0, RP=1, PP=0

0A> Reset

01F00C04 00000000

0A> Error

01F00E00 00000000 00000000

0A> ME=0, XP=0, CC=0, VP=0, AE=0, EV=0, CCOP=0, ERR=0, S=0, PA=0 00000000

0A> CompId

01F00F04 02000104

0A> MID=2, MDEV=1, MREV=0, MVEND=4

```

```

0A>Probing 09F00000

0A> CC Register Base09F00000

0A> StreamData

OA> Stream Data[0] 09F00000 00000000 00000000

0A> Stream Data[1] 09F00008 00000000 00000000

OA> Stream Data[2] 09F00010 00000000 00000000

OA> Stream Data[3] 09F00018 00000000 00000000

OA> Stream Data[4] 09F00020 00000000 00000000

OA> Stream Data[5] 09F00028 00000000 00000000

0A> Stream Data[6] 09F00030 00000000 00000000

0A> Stream Data[7] 09F00038 00000000 00000000

0A> StreamSrcAddr 09F00100 80000000 00000000

0A> StreamDstAddr 09F00200 80000010 1D555FC0

0A> RefMissCnt

09F00300 00000000 00000000

09F00406

0

0A> IntrptPend

0A> IntrptMask

09F00506 FFFE

0A> BIST

09F00804 23AA97E6

0A> Control

09F00A04 0000002C

0A> RC=0, DCB=0, WI=0, PF=1, MC=0, PE=1, CE=1, CS_HC=0

0A> Status

09F00B00 0000000F FFF00000

0A> SXP=0, SM=0, NCSID=0, NCSPA=FFFF00 NCSPC=0, SPC=0, BC=0, WP=0, RP=0, PP=0

0A> Reset

09F00C04 00000000

0A> Error

09F00E00 00000000 00000000

0A> ME=0, XP=0, CC=0, VP=0, AE=0, EV=0, CCOP=0, ERR=0, S=0, PA=0 00000000

09F00F04 00000104

0A> CompId

0A> MID=0, MDEV=1, MREV=0, MVEND=4

0A>Probing E0100000

0A>MOH Register Base E0100000

0A>

Comp ID

10D8607D

0A>

DCSR

00048700.1000D000

0A>

DDR

FFFFFFFF, FFFFFFFF

0A>

G0ADR

02400009

0A>

G1ADR

02000009

0A>

G2ADR

00000000

G3ADR

0A>

00000000

0A>

GOTYPE

08000800.08000800

0A>

G1TYPE

08000800.08000800

0A>

G2TYPE

FFFFFFFF.FFFFFFF

0A>

G3TYPE

FFFFFFFF.FFFFFFF

0A>

MCSR

00000000.00024101

0A>

CEADR

294C4000.00F90800

0A>

CEDR

0000000.0000000

0A>

UEADR

2940C000.00F90800

0A>

UEDR

0000000.0000000

0A>

ECCDCR

00000000,00000000

```

```

0A>

Timing Registers

0A>

00000000.00000141

0A>

00000000.00000021

0A>

00000000.0000022D

0A>

00000000.000004AF

0A>

00000000.00000147

0A>

00000000.00000117

00000000.0000021B

0A>

0A>

A8000000.0000008A

0A>

00000000.00000002

0A>

00000000.00000012

0A>

0000000.00000090

0A>

00000000.00000040

0A>

0000000.0000000

0A>

0000000.0000000

0000000.0000000

0A>

0A>

0000000.0000000

0A>

0000000.0000000

0A>

00000000.00000000

0A>

0000000.0000000

0A>

0000000.0000000

0A>Probing E0200000

0A>IOC Register Base E0200000

0A>

Comp ID

10ADD07D

0A>

DCSR

0001A000.2000DD00

0A>

DDR

FFFFFFFF.FFFFFFF

CTL

0A>

0001E060

0A>

DBUS Tags SBUS Tags State Bits

0A>

00000000

00000000

00000000

0A>

00000000

00000000

00000000

0A>

00000000

00000000

00000000

0A>

00000000

00000000

00000000

```

```

0A>Probing 02800000

0A>SBI Register Base 02800000

Comp ID

0A>

20ADE07D

0A>

CTL

00020000

0A>

SR

0000000

0A>

SOCR

00000021

0A>

S1CR

00000021

0A>

S2CR

00000021

0A>

S3CR

00000021

0A>

SOSBCR

0000000

0A>

S1SBCR

0000000

0A>

S2SBCR

0000000

0A>

S3SBCR

0000000

0A>

ISR

0000000

0A>

ITIDR

00000000

OA>Hit any key to continue :

System Parameters

OA>Select one of the following functions

`O'

0A>

Set POST Level

0A>

11'

Dump Device Table

0A>

12′

Display System

0A>

١3 ′

Dump Board Registers

0A>

۱4′

Dump Component IDs

۱5′

0A>

Clear Error Logs

0A>

۱6′

Display Simms

۱7′

0A>

Scrub Main Memory

0A>

'r'

Return

Command ==> 4

```

| A> Ring             | bic0       | bic1     | bic2            | bic3            | barb     |

|---------------------|------------|----------|-----------------|-----------------|----------|

| )A>++<br>)A> 0,1    |            |          | +<br>  30ADA07D | +<br>  30ADA07D | 20AD907D |

| )A> 1,1             | 30ADA07D   | 30ADA07D | 30ADA07D        | 30ADA07D        | 20AD907D |

| )A> 2,1             | 30ADA07D   | 30ADA07D | 30ADA07D        | 30ADA07D        | 20AD907D |

| )A>++               |            | ++       | +               | ++              | +        |

|                     | sor A Ring |          | +               | +               |          |

| )A> Ring            |            | mxccA    | bwA             |                 |          |

| )A>++               |            | +        | +               | ++              | +        |

| DA> 0,2             | 0000402F   | 0000302F | 10D3907D        |                 |          |

| DA> 1,2             | 0000402F   | 0000302F | 10D3907D        |                 |          |

| , ,                 | 0000402F   | 0000302F |                 |                 |          |

|                     |            | +        | +               | ++              | +        |

| )A> Memory<br>)A>++ |            | +        | <b>.</b>        | <b>.</b>        |          |

| A> Ring             | mgh        |          | ·<br>           |                 | ·<br>    |

| - 1                 |            | <br>     | <br>            | ı<br>+          | <br>     |

| DA> 0,3             | 10D8607D   |          |                 |                 |          |

| )A> 1,3             | 20D8607D   |          |                 |                 |          |

| :                   | 10D8607D   | <br>     |                 |                 |          |

| )A>++               |            | +        | +               | +               |          |

| OA> IO Rin          | ıg(s)      |          |                 |                 |          |

| )A>++               |            | +        | +               | +               | +        |

| DA> Ring            | sbi        | ioc      |                 |                 |          |

| )A>++               |            | +        | +               | +               |          |

| , ,                 | 20ADE07D   |          |                 |                 |          |

| DA> 1,4             |            | 10ADD07D |                 |                 |          |

| DA> 2,4             |            | 10ADD07D | <u> </u>        |                 |          |

| )A>++               | sor B Ring | +        | +               | +               |          |

|                     | _          | (S)<br>+ | +               | +               |          |

| DA> Ring            |            | mxccB    |                 |                 | ·<br>    |

| )A>++               |            | +        |                 | +               |          |

| DA> 0,5             | 0000402F   | 0000302F | 10D3907D        |                 |          |

| )A> 1,5             | FFFFFFFF   | FFFFFFFF | FFFFFFF         |                 |          |

| DA> 2,5             | FFFFFFFF   | FFFFFFFF | FFFFFFFF        |                 |          |

| 77 ~ 1              |            | +        |                 |                 |          |

```

System Parameters

OA>Select one of the following functions

0A>

` 0 '

Set POST Level

111

0A>

Dump Device Table

0A>

121

Display System

0A>

۱3′

Dump Board Registers

١4 ′

0A>

Dump Component IDs

0A>

`5'

Clear Error Logs

0A>

۱6′

Display Simms

0A>

`7'

Scrub Main Memory

`r'

0A>

Return

Command ==> 6

0A>Which Board (a = all boards)? 0

0A>

DRAM

NVRAM

Size

Size

Speed

Speed | Manufacturer

0 | 4Mbit | 80ns |

1Mbit

70ns |

1 | 16Mbit | 100ns | 4Mbit | 85ns |

MS

2 | 64Mbit | - | - |

{If NVSIMM, NV=1 and B=1 if battery is good}

0A>Board 0 SIMM Map

0A> SIMM|Grp|Data | ECC|Size|Spd|Mfq|B|NV| SIMM|Grp|Data | ECC|Size|Spd|Mfq|B|NV|

OA> 4100 3 31:16 3:2

4300 3 63:48 7:6

OA> 3700 2 31:16 3:2

3900 2 63:48 7:6

OA> 3300 1 31:16 3:2

2 0 0 3500 1 63:48 7:6 0

2 0 0 3100 0 63:48 7:6

OA> 2900 O 31:16 3:2

0 0

0A> 4000 3 15:00 1:0

4200 3 47:32 5:4

0A> 3600 2 15:00 1:0

3800 2 47:32 5:4

OA> 3200 1 15:00 1:0

0 0

2 0 0 3400 1 47:32 5:4 0

0

2 0 0

0 0 2 0 0 3000 0 47:32 5:4 0 0 2 0 0

OA>Hit any key to continue :

0A>

```

```

System Parameters

OA>Select one of the following functions

`O'

Set POST Level

0A>

0A>

11'

Dump Device Table

0A>

12'

Display System

0A>

١31

Dump Board Registers

۱4′

0A>

Dump Component IDs

0A>

۱5′

Clear Error Logs

0A>

۱6′

Display Simms

0A>

۱7′

Scrub Main Memory

0A>

`r'

Return

Command ==> 7

OA>Hit any key to continue :

0A>

System Parameters

OA>Select one of the following functions

`O'

0A>

Set POST Level

0A>

11′

Dump Device Table

12'

0A>

Display System

131

0A>

Dump Board Registers

0A>

۱4′

Dump Component IDs

0A>

`5'

Clear Error Logs

0A>

۱6′

Display Simms

۱7′

0A>

Scrub Main Memory

0A>

'r'

Return

Command ==> r

0A>

DEMON

OA>Select one of the following functions

0A>

`O'

System Parameters

0A>

11'

Read/Write device

121

0A>

Software Reset

١3 ′

0A>

NVRAM Management

0A>

۱4′

Error Reporting

0A>

`5'

Analyze Error Logs

0A>

۱6′

Power Off at Main Breaker

0A>

`7'

NVRAM SIMM tests

0A>

'r'

Return to selftest

0A>

Command ==> 1

```

```

0A>rwdev> ?

0A>General command format is:

op_size_space asi address data count increment

op = r or w or q (read or write or quit)

size = b,h,w or d

space = a or v (alternate or virtual space)

asi = 2 - 0x4c (if alternate space)

address = device or memory address

data = write data (if write)

count = optional range count

increment = optional address increment (default is data type)

NOTE: '.'s are ignored and can be used as seperators.

Examples:

rwdev> wba 2f f01e.0000 a5 4 /* writes 4 consecutive bytes into bootbus SRAM */

rwdev> rdv 0 10 /* reads the frist 16 doublewords from cachable space */

rwdev> rda 2 0180.0000 4 100 /* reads the first 4 MXCC tags */

rwdev> rwa 2f fff0.3010 40 0 /* reads the BW tick timer 64 times */

0A>rwdev> q

0A>

DEMON

OA>Select one of the following functions

0A>

`O'

System Parameters

0A>

11'

Read/Write device

12′

0A>

Software Reset

0A>

۱3′

NVRAM Management

۱4′

0A>

Error Reporting

`5'

0A>

Analyze Error Logs

۱6′

0A>

Power Off at Main Breaker

0A>

`7'

NVRAM SIMM tests

0A>

'r'

Return to selftest

0A>

Command ==> 2

OA>Initiating Software Reset...

```

```

0A>

DEMON

OA>Select one of the following functions

`O'

0A>

System Parameters

0A>

11'

Read/Write device

0A>

`2'

Software Reset

۱3′

0A>

NVRAM Management

۱4′

0A>

Error Reporting

0A>

`5'

Analyze Error Logs

0A>

۱6′

Power Off at Main Breaker

`7'

0A>

NVRAM SIMM tests

0A>

`r'

Return to selftest

0A>

Command ==> 3

0A>

Bootbus NVRAM Management

OA>Select one of the following functions

0A>

۱0′

Print Bad Group List

0A>

11'

Clear Bad Group List

0A>

121

Print Bad Page List

0A>

۱3′

Clear Bad Page List

0A>

r'

Return to Main menu

0A>

Command ==> 0

0A>Bad Memory Groups on System

0A>No Bad groups found

OA>Hit any key to continue :

0A>

Bootbus NVRAM Management

OA>Select one of the following functions

` O '

0A>

Print Bad Group List

11'

0A>

Clear Bad Group List

0A>

`2'

Print Bad Page List

0A>

۱3′

Clear Bad Page List

0A>

`r′

Return to Main menu

0A>

Command ==> 2

0A>Bad Memory Pages in System

0A>No Bad pages found

OA>Hit any key to continue :

```

```

0A>

Bootbus NVRAM Management

OA>Select one of the following functions

0A>

` 0 '

Print Bad Group List

11'

0A>

Clear Bad Group List

0A>

12'

Print Bad Page List

۱3′

0A>

Clear Bad Page List

0A>

`r′

Return to Main menu

0A>

Command ==> r

0A>

DEMON

OA>Select one of the following functions

0A>

`O'

System Parameters

0A>

11'

Read/Write device

121

0A>

Software Reset

137

0A>

NVRAM Management

۱4′

0A>

Error Reporting

0A>

`5'

Analyze Error Logs

0A>

۱6′

Power Off at Main Breaker

0A>

`7'

NVRAM SIMM tests

0A>

\r'

Return to selftest

0A>

Command ==> 4

0A>

Dump Error Reset Status

0A>

'0' - '3' Select Board

0A>

'r'

Return

Command ==> 0

0A>Dumping local board 0

0A>Log Date: Mar 17 0:14:53 GMT 1993

0A>A CC Error Register = 00000000.00000000

0A>B CC Error Register = 00000000.00000000

0A>Processor A

0A>BW0 DCSR = 0001A000.0800DD10 DDR = 00000000.00002000

0A>Processor B

0A>BWO DCSR = 00FFF0FF.FFFFFFF DDR = FFFFFFFF.FFFFFFF

0A>MOHO DCSR = 00048700.1800D090 DDR = 00000000.00002000

0A>IOCO DCSR = 0001A000.2800DD90 DDR = 00000000.00002000

0A>SBI Control = 00020000 Status = 00000000

0A>Analyzing BIC data

```

```

0A>XDBus 0 on ***BOARD*** caused parity error

OA>History log bit 12 shows failed BICs : BIC 0, Byte 1;

OA>Hit any key to continue :

0A>

Dump Error Reset Status

'0' - '3' Select Board

0A>

'r'

0A>

Return

Command ==> r

0A>

DEMON

OA>Select one of the following functions

` O '

System Parameters

0A>

0A>

11'

Read/Write device

12′

Software Reset

0A>

0A>

١3 ′

NVRAM Management

۱4′

Error Reporting

0A>

`5'

0A>

Analyze Error Logs

0A>

۱6′

Power Off at Main Breaker

`7'

0A>

NVRAM SIMM tests

`r′

Return to selftest

0A>

0A>

Command ==> 5

0A>

----- Error Log Analysis for Board 0 ------

0A>*BW0 (CPU A)

0A> XDBus Parity Error, XDBus Data = 00000000.00002000 XDBus Parity = 00

0A>*MOH0

0A> Multiple Errors

0A> XDBus Parity Error, XDBus Data = 00000000.00002000 XDBus Parity = 00

0A>*IOC0

0A> Multiple Errors

0A> XDBus Parity Error, XDBus Data = 00000000.00002000 XDBus Parity = 00

0A>XDBus 0 on ***BOARD*** caused parity error

OA>History log bit 12 shows failed BICs : BIC 0, Byte 1;

OA>Log Date: Mar 17 0:14:53 GMT 1993

0A>CPU A Function at time of error: System Level Software

OA>CPU B Function at time of error: System Level Software

0A>

```

```

----- Error Log Analysis for Board 1 ------

0A>*BW0 (CPU A)

0A> XDBus Parity Error, XDBus Data = 00000000.00002000 XDBus Parity = 00

0A>*MOH0

0A> Multiple Errors

0A> XDBus Parity Error, XDBus Data = 00000000.00002000 XDBus Parity = 00

0A>*IOC0

0A> Multiple Errors

0A> XDBus Parity Error, XDBus Data = 00000000.00002000 XDBus Parity = 00

0A>XDBus 0 on ***BACKPLANE*** caused parity error

OA>History log bit 13 shows failed BICs : BIC 0, Byte 1;

OA>Log Date: Mar 17 0:16:12 GMT 1993

0A>CPU A Function at time of error: System Level Software

----- Error Log Analysis for Non-Processor Board 2 -----

OA>Parity error on XDBus O caused by ***BACKPLANE***

OA>Parity error detected by BIC 2 byte 1

OA>Log Date: Mar 17 0:14:53 GMT 1993

----- System Memory Failure Analysis ------

0A> No Bad groups found

OA>Hit any key to continue :

0A>

DEMON

OA>Select one of the following functions

0A>

` O '

System Parameters

11'

0A>

Read/Write device

121

0A>

Software Reset

۱3′

0A>

NVRAM Management

0A>

۱4′

Error Reporting

151

0A>

Analyze Error Logs

0A>

۱6′

Power Off at Main Breaker

0A>

۱7′

NVRAM SIMM tests

0A>

'r'

Return to selftest

0A>

Command ==> 7

0A>

```

```

NVRAM SIMM Tests

OA>Select one of the following functions

Read-Write 6N Test

0A>

` O '

11′

0A>

Write Test (no verify)

0A>

12'

Read Test (verify single pattern)

0A>

`r′

Return to Main menu

0A>

Command ==> 0

0A>NVRAM 6N Read-Write Test

0A>Couldn't find any NVRAM

OA>Hit any key to continue :

0A>

NVRAM SIMM Tests

OA>Select one of the following functions

0A>

`0'

Read-Write 6N Test

0A>

11'

Write Test (no verify)

12′

Read Test (verify single pattern)

0A>

Return to Main menu

0A>

`r′

0A>

Command ==> r

0A>

DEMON

OA>Select one of the following functions

0A>

۱0′

System Parameters

11'

Read/Write device

0A>

121

0A>

Software Reset

۱3′

0A>

NVRAM Management

۱4′

0A>

Error Reporting

151

0A>

Analyze Error Logs

Power Off at Main Breaker

0A>

۱6′

0A>

۱7′

NVRAM SIMM tests

0A>

`r'

Return to selftest

0A>

Command ==> r

0A>

```

# Test Descriptions

This chapter contains the descriptions for the tests that make up the POST software.

**Note** – This chapter lists the tests *in the order in which they are executed* when POST is invoked.

The general format for each test description is as follows.

Each test has an LED pattern (shown as a set of eight lights) associated with it. The hexadecimal value of this LED pattern is also shown alongside the test name. A brief description of the test follows, along with the test ID number, attributes, and a diagnosis field showing the possible cause of a problem (should a test fail).

For test LED patterns in this manual, white lights ( $\bigcirc$ ) indicate that the LED is OFF, and black lights ( $\bullet$ ) indicate that the LED is ON.

The description of the test is followed by descriptions for each of the subtests within a test. Like tests, subtests also show IDs, attributes, diagnoses, and brief descriptions of the functions they perform. In addition, the algorithm (in the form of pseudocode) and the error messages for each subtest are also listed. Subtests do not have hexadecimal values (and their corresponding LED patterns) associated with them.

# 2.1 Early POST Tests

Shortly after power-on and before transferring control to the test sequencers (see Appendix B), POST does a few preliminary tests. These tests are basic checks to verify that the CPU and BootBus are working well enough so that POST can begin more comprehensive testing.

The following tests are very basic; if they fail, you may or may not see error messages (depending on the extent of the failure).

- The first check is to start BIST (built-in self-test) on the MXCC ASIC. The BIST takes one second to execute. If this operation hangs the CPU, you see the value 0x01 in the board LED display.

- The next check is to start BIST on the CPU module. This BIST takes one second to execute. If this operation hangs the CPU, you see the value 0x02 in the board LED display.

**Note** – If POST is running in diag mode, it displays the resultant BIST signatures.

- POST now does a basic BootBus NVRAM read/write test. POST tests 8 bytes of NVRAM at the NVRAM base address +8. If it detects a failure, POST attempts to print a message on TTYA, then falls into and remains in a write/read scope loop for as long as the failure persists. If this test fails, you see the value 0x04 in the LEDs. This is a non-destructive test; POST saves the 8 bytes prior to the test and later restores them.

- Finally, POST does a basic BootBus SRAM read/write test. POST tests 8 bytes of SRAM at the SRAM base address +8. If a failure is detected, POST attempts to print a message on TTYA, then falls into and remains in a write/read scope loop for as long as the failure persists. If this test fails, you see the value 0x05 in the LEDs. This is a non-destructive test; POST saves the 8 bytes prior to the test and later restores them.

0x06

# 2.2 Board Level Testing

The following series of tests verify all functional elements of CPU A, CPU B, the System Board components (Bootbus, BW's, IOC's, SBI, MQH's) and all memory present on this board. These tests are run while all System Boards are in XDBus loopback.

# ○○○○ ○●○○ EPROMS

• ID: 6.0

Attributes: C0 Mandatory Test

Diagnosis: BootBus

Test the BootBus EPROM.

# Subtest: EPROM path

ID: 6.1 Level: 17

Attributes: Test Module

Initialization Module

Fetch previously stored data from the EPROM, and verify that the correct byte, halfword, and word data gets fetched.

- Test byte access.

- Test halfword access.

- · Test word access.

- Test doubleword access.

#### Possible Error Messages

```

Data Compare Error

address = %X

expected = %X

observed = %X

```

Subtest: EPROM checksum

ID: 6.2Level: 17

• Attributes: Test Module

Initialization Module

Compute a checksum for all addresses of the PROM except the last two bytes of each PROM. Read the last two bytes, and compare the calculated value with the observed one. If an error occurs, a message indicates the failing byte.

# Possible Error Messages

EPROM %d checksum error exp=0x%X obs=0x%X

0000 ●000 LEDs 0x08

• ID: 8.0

• Attributes: C0 Useful Test

• Diagnosis: BootBus

Test the BootBus LED Register.

Subtest: WALK LED

• ID: 8.1 • Level: 8

Attributes: Test Module

Walk 1s through the LED register.

- · Clear all LEDs.

- Sequentially light up LEDs from right to left or bottom to top.

Possible Error Messages

This test does not report any errors.

# OOOO ●OO● Serial Ports

0x09

• ID: 9.0

• Attributes: C0 Useful Test

• Diagnosis: BootBus

Test the BootBus Serial Communication Control serial ports.

Subtest: Port A Register

• ID: 9.1 • Level: 17

• Attributes: Test Module

Perform a Walking 1s test on the UART SCC (Z85C30) write/read register 12.

# Possible Error Messages

```

Data Compare Error

address = %X

expected = %X

observed = %X

```

# Subtest: Port B Register

• ID: 9.1 • Level: 17

• Attributes: Test Module

Perform a Walking 1s test on the UART SCC (Z85C30) write/read register 12.

# Possible Error Messages

```

Data Compare Error

address = %X

expected = %X

observed = %X

```

# Subtest: Serial Port A Loopback

ID: 9.2Level: 17

• Attributes: Test Module

### Test Serial Port A using loopback.

- Initialize the UART and enable loopback.

- Send characters 0x20 through 0x7f.

- Check RXRDY and verify that RXDATA = TXDATA.

### Possible Error Messages

```

pa=%x local loopback error no txready

pa=%X local loopback error no rxready

pa=%X local loopback error exp=0x%X, obs=0x%X

```

# Subtest: Serial Port B Loopback

ID: 9.3 Level: 17

Attributes: Test Module

#### Test Serial Port B using loopback.

- Initialize the UART and enable loopback.

- Send characters 0x20 through 0x7f.

- Check RXRDY and verify that RXDATA = TXDATA.

# Possible Error Messages

```

pa=%x local loopback error no txready

pa=%X local loopback error no rxready

pa=%X local loopback error exp=0x%X, obs=0x%X

```

# ○○○○ ●○●● Keybd/Mouse

0x0B

• ID: 11.0

Attributes: C0 Useful TestDiagnosis: BootBus

Test the BootBus Serial Communication Control keyboard and mouse ports.

Subtest: Keyboard Loopback

• ID: 11.1 • Level: 8

Attributes: Test Module

Test the keyboard using loopback.

- Initialize the UART and enable loopback.

- Send characters 0x20 through 0x7f.

- Check RXRDY and verify that RXDATA = TXDATA.

### Possible Error Messages

pa=%x local loopback error no txready

pa=%X local loopback error no rxready

pa=%X local loopback error exp=0x%X, obs=0x%X

# Subtest: Mouse Loopback

• ID: 11.2 • Level: 8

• Attributes: Test Module

Test the mouse using loopback.

- Initialize the UART and enable loopback.

- Send characters 0x20 through 0x7f.

- Check RXRDY and verify that RXDATA = TXDATA.

pa=%x local loopback error no txready

pa=%X local loopback error no rxready

pa=%X local loopback error exp=0x%X, obs=0x%X

OOOO ••OO NVRAM/TOD

0x0C

- ID: 12.0

- Attributes: C0 Useful TestDiagnosis: BootBus

Test the BootBus NVRAM time-of-day clock function to insure that the clock is running.

OOOO ●●○● Basic CPU

0x0D

- ID: 13.0

- Attributes: General Purpose

Diagnosis: CPUA Module

**CPUB Module**

Test the Basic CPU functions.

Subtest: FPU Register

• ID: 13.1 • Level: 8

• Attributes: Test Module

Initialization Module

Test floating-point unit registers.

- Read a data pattern into an FPU register.

- Write FPU register out to memory.

- Compare data in memory to original data.

- Repeat for all FPU registers.

- Repeat for several data patterns.

Unexpected trap occurred during FPU operation

FPU Double Reg %d, exp %X %X, obs %X %X, reg, exp, obs

Single Precision, exp = %X, obs = %X

### Subtest: FPU Functional

- ID: 13.1 • Level: 8

- Attributes: Test Module Initialization Module

Test the functionality of the floating-point unit.

- Perform the following operation, using single precision: (((3\*4\*5)-2+2)/4)/5.

- Verify that the result is 3.0.

- Repeat, using double precision.

### Possible Error Messages

Unexpected trap occurred during FPU operation

FPU Double Reg %d, exp %X %X, obs %X %X, reg, exp, obs

Single Precision, exp = %X, obs = %X

#### Subtest: MMU TLB

- ID: 13.1 • Level: 17

- Attributes: Test Module

Subtest Disabled Initialization Module

Write-read-verify all TLB entries using Walking 1s pattern.

# Possible Error Messages

unexptd\_tlb\_msg, entry, sel, exp, obs)

Subtest: Instruction Cache Tags

ID: 13.1 Level: 17

• Attributes: Test Module

Initialization Module

Test that the Icache can be flash-cleared and that the tags can be addressed uniquely. Also check the tag array for data reliability.

- Write all the state bits and an incrementing pattern in the Paddr field.

- Flash clear the lock bits; check thatthey get cleared and that Paddr is not changed.

- Flash clear the valid and mru bits; check that all valid and mru bits are clear and that lock bits and Paddr field are unchanged.

## Possible Error Messages

```

Data Compare Error

address = %X

expected = %X.%X

observed = %X.%X

```

# Subtest: Instruction Cache Ram

• ID: 13.2 • Level: 17

Attributes: Test Module

Initialization Module

Test the instruction cache RAM.

# Address Ascending:

- · Write each address with its address as the data.

- Read and verify each address.

# Address Descending:

- · Write each address with its address as the data.

- Read and verify each address.

#### Cell Disturbance:

- Write the entire cache with a checkerboard bit pattern.

- · Read and verify each address.

- Reverse the checkerboard pattern and repeat.

# Data Reliability:

- Write the cache with standard test patterns.

- · Read and verify the data.

### Possible Error Messages

```

Data Compare Error

address = %X

expected = %X.%X

observed = %X.%X

```

### Subtest: Data Cache Tags

• ID: 13.3 • Level: 8

• Attributes: Test Module

**Initialization Module**

Test the CPU's data cache tags for address uniqueness and data reliability.

# Address Ascending:

- Write each tag with its address as the data.

- Read and verify each address.

# Address Descending:

- · Write each address with its address as the data.

- Read and verify each address.

#### Cell Disturbance:

- Write the entire array with a checkerboard bit pattern.

- · Read and verify each address.

- Reverse the checkerboard pattern and repeat.

# Data Reliability:

- Write the tag array with standard test patterns.

- Read and verify the data.

```

Data Compare Error

address = %X

expected = %X.%X

observed = %X.%X

```

### Subtest: Data Cache Ram

• ID: 13.4 • Level: 8

• Attributes: Test Module

**Initialization Module**

Test address uniqueness and data reliability of the CPU internal data cache RAMs.

# Address Ascending:

- · Write each address with its address as the data.

- Read and verify each address.

# Address Descending:

- · Write each address with its address as the data.

- Read and verify each address.

#### Cell Disturbance:

- Write the entire cache with a checkerboard bit pattern.

- Read and verify each address.

- Reverse the checkerboard pattern and repeat.

# Data Reliability:

- Write the cache with standard test patterns.

- Read and verify the data.

# Possible Error Messages

```

Data Compare Error

address = %X

expected = %X.%X

observed = %X.%X

```

Subtest: Store Buffer Tags

ID: 13.5 Level: 8

• Attributes: Test Module

Initialization Module

Verify Store Buffer tags for address uniqueness and data reliability. (The test is run with the Store Buffer off.)

Store Buffer Addressing test:

- · Write address ascending.

- · Read and verify.

- Write address descending.

- Read and verify.

Store Buffer RAM data reliability:

- Write all tags with test pattern.

- · Read each tag and verify data.

- · Loop for all patterns.

### Possible Error Messages

Data Compare Error

address = %X

expected = %X.%X

observed = %X.%X

#### Subtest: Store Buffer RAM

• ID: 13.6 • Level: 8

• Attributes: Test Module

Initialization Module

Verify Store Buffer SRAMs for address uniqueness and data reliability. (This test is run with the Store Buffer off.)

# Store Buffer Addressing test:

- Write address ascending.

- Read and verify.

- · Write address descending.

- · Read and verify.

### Store Buffer RAM data reliability:

- Write entire RAM with test pattern.

- · Read RAM and verify the data.

- Loop for all patterns.

#### Possible Error Messages

```

Data Compare Error

address = %X

expected = %X.%X

observed = %X.%X

```

# Subtest: Store Buffer Functional

• ID: 13.9 • Level: 8

• Attributes: Test Module

Initialization Module

Test the Store Buffer functions that can be tested while in boot mode with the Ecache turned off. (Implies only non-cacheable space.)

This test currently issues stores to EPROM address space. The actual results are obtained from the Store Buffer.

Stress test using non-cacheable stores:

- Make sure Store Buffer is off.

- Zero Store Buffer control and all tags.

- Clear the tags.

(The Dptr and Fptr are set to 0.)

- Turn on Store Buffer.

- Issue 8 stores that should use each entry in the Store Buffer (0..7).

- Turn off Store Buffer.

- Read the tags and data, and verify.

Using EPROM address space, float 1 through the address field of each tag:

- Issue the store.

- Read the tag and data.

- Float address bit, and loop for all address bits.

Use a bus parity error to force a Store Buffer error, and check the Store Buffer tags, data, and control for proper state:

- Establish the trap handler. (The first store will go to the Store Buffer. The load will cause the Store Buffer to flush this store with odd parity. The MXCC should complain about the bad parity. The CPU should take a data store error trap.)

- Check that the correct trap (data store error) occurs.

(Dptr must point to the entry that incurred the data store error.)

- · Check the Store Buffer control and tags.

- Zero Store Buffer control and all tags .

#### Possible Error Messages

```

Store Buffer tag error

entry = %x

expected = %X.%X

observed = %X.%X

Store Buffer data error

entry = %x

expected = %X.%X

observed = %X.%X

Store Buffer control error

expected = %X

observed = %X

Data store error trap did not occur

```

# Subtest: MXCC Registers

• ID: 13.10 • Level: 8

• Attributes: Test Module

Initialization Module

Test the read and write accessibility of the MXCC ASIC registers, using all access sizes allowed. The addresses of the MXCC registers are in ECSR space and Control Space (ASI 2).

To prevent XDBus transactions, this test uses Control Space Access only. If any access causes a data access exception or unexpected interrupt, the test aborts with a FAIL status.

The Stream Source and Destination Address registers are not tested here (because they generate XDBus transactions to the BWs), but they are tested after the rest of the system is initialized and tested. Also, the Interrupt registers must be tested later, because they generate XDBus transactions to the BW.

A write to the Status register has bad side effects (it can cause the CPU to hang). So it is not tested except to read it and insure that it does not cause a trap.

The Reset register is tested by clearing it and verifying that it clears. A Software Reset can be tested from the DEMON Menu.

The Error register is read only. The test clears all errors then checks to insure that all error bits are cleared.

#### Possible Error Messages

```

%s register value indicates XBus may be broken

expected = %X.%X

observed = %X.%X

While testing %s register an unexpected trap occurred

MFSR = %X

MFAR = %X

Trap Type = %2x

CC Error = %X.%X

```

```

Unexpected Component ID value

address = %X

expected = %X or %X

observed = %X

%s register failed to return correct data

address = %X

expected = %X

observed = %X

%s register failed to return correct data

expected = %X.%X

observed = %X.%X

Floating a bit through %s register failed

expected = %X

observed = %X

Floating a bit through %s register failed

expected = %X.%X

observed = %X.%X

```

# Subtest: Init MXCC Regs

• ID: 13.11 • Level: 8

• Attributes: Error is Fatal

Clear the MXCC error register, clear all pending interrupts, clear the reference/miss count register, and enable Level 15 interrupts.

Possible Error Messages

This module does not check or report errors.

# 0000 ●●●0 Ecache 0x0E

• ID: 14.0

Attributes: C0 Useful Test

Diagnosis: CPUA Module CPUB Module

Test the external cache system.

Subtest: Setting Cache Size

• ID: 14.1 • Level: 1

• Attributes: Error is Fatal

Set or clear the bits for the selected mode, half or full cache.

Possible Error Messages

This module does not check or report errors.

Subtest: Ecache Tags

• ID: 14.2 • Level: 8

• Attributes: Test Module

Initialization Module

Test address uniqueness and data reliability of the external cache (MXCC) tags.

- Do a write pass in ascending order.

- Do a read pass in ascending order.

- Do a write pass in descending order.

- Do a read pass in descending order.

- Do the data reliability test case.

- Loop through all the patterns.

## Possible Error Messages

```

Data Compare Error

address = %X

expected = %X.%X

observed = %X.%X

```

Subtest: Ecache SRAM

• ID: 14.3 • Level: 8

• Attributes: Test Module

Initialization Module

Test access size, addressing, and SRAM data reliability. (This test is run with the external cache disabled.)

#### Test CC SRAM access:

- Write a pattern into an SRAM double word location.

- Read it back a byte at a time and verify.

- Read it back a half at a time and verify.

- · Read it back a word at a time and verify.

- Write every byte in the cache line.

- · Read and verify.

- · Write every half in the cache line.

- Read and verify.

- Write every word in the cache line.

- · Read and verify.

# Test CC SRAM addressing:

- Write pass address up.

- · Read pass address up.

- · Write pass address down.

- Read pass address down.

# Test CC SRAM data reliability:

- Only do the long test if POST LEVEL is high.

- Loop through all the patterns. (Checking for stuck ats.)

- Test pattern and ~pattern.

- Turn on CPU module Bus parity and watch for traps.

- Set up trap to handle data access exception (parity error).

- · Loop through all patterns.

- · Check for parity error.

- Check for miscompares.

# Do a short test for booting (DIAG Switch OFF):

- Turn on CPU module Bus parity and watch for traps.

- Set up g5 and g6 to expect data access exception.

- Write pass; write alternate patterns.

- Loop through the cache, comparing alternate patterns.

- Check for parity error.

- Check for miscompares.

- Repeat test with mixed parity patterns.

```

Viking Parity Error

address = %X

expected = %X.%X

observed = %X.%X

Data XOR = %X.%X

Part = U%d

```

# Subtest: Ecache Enable

• ID: 14.5 • Level: 1

• Attributes: Error is Fatal

Enable the external cache.

(From this point on, the cache remains enabled.)

# Possible Error Messages

This module does not check or report errors.

#### Subtest: Clear CC SRAM

• ID: 14.4 • Level: 1

• Attributes: Error is Fatal

Clear the external cache SRAM.

(This also insures that good parity is established for the SRAM.)

### Possible Error Messages

This module does not check or report errors.

0x12

• ID: 18.0

• Attributes: C0 Mandatory Test

• Diagnosis: BWA0

BWB0

Test the registers and tags on Bus Watcher 0.

Subtest: C\_O BW

ID: 18.1 Level: 1

• Attributes: Initialization Module

Error is Fatal

Establish the board configuration for this test.

Possible Error Messages

This module does not check or report errors.

Subtest: BW Registers

ID: 18.2 Level: 8

• Attributes: Test Module

Initialization Module

Test the read and write accessibility of all BW ASIC registers, using all access sizes allowed. The addresses of the BW registers are in CSR space and Local space; the test uses both address spaces. If any access causes a data access exception or unexpected interrupt, the test aborts with a FAIL status.

# Possible Error Messages

```

While testing %s register an unexpected trap occurred

MFSR = %X

MFAR = %X

Trap Type = %2x

CC Error = %X.%X

```

Unexpected Component ID value address = %X expected = %X or %X observed = %X %s register failed to return correct data address = %X expected = %X observed = %X %s register failed to return correct data expected = %X.%X observed = %X.%X Floating a bit through %s register failed expected = %X observed = %X Floating a bit through %s register failed expected = %X.%X observed = %X.%X

# Subtest: Timers and Interrupts

• ID: 18.3 • Level: 8

• Attributes: Test Module

**Initialization Module**

Test timer in free running mode, no interrupts.

- Make sure the prescaler is initialized for 1 microsecond.

- Configure Ptimer for non-UT mode.

- First do the Ptimer, then do the Ttimer.

- Clear all interrupt registers.

- Set timer to run free.

- Stall for a few milliseconds.

- Make sure the counter did some counting.

- Check the interrupt table (should be 0).

Test both P and T timer in limit mode with interrupts.

- First do the Ptimer, then do the Ttimer.

- Set timer to run free.

- Clear all interrupt registers.

- Set limit to 100 and see if interrupt is generated.

- Stall for a few milliseconds.

- · Check the limit bits.

- Check the interrupt table.

- Check the interrupt pending.

- Setup for tick timer.

- Set timer to free running mode turn off interrupts.

#### Test User Timer Mode.

- Configure the Ptimer for User Timer mode.

- Make sure it counts.

# Test alarm clock interrupts.

- First do the Ptimer, then do the Ttimer.

- Set timer to run free.

- Clear all interrupt registers.

- Set ND limit to 100 and see if interrupt is generated.

- Stall for a few milliseconds.

- Check the limit bits.

- · Check the interrupt table.

- Check the interupt pending.

- Setup for tick timer.

- Set timer to free running mode turn off interrupts.

# Clean up everything.

- Configure Ptimer for non-UT mode.

- Set timer to run free.

- Clean up interrupt registers.

# Possible Error Messages

```

Timer Free Running Mode Error

Address = %X

start count = %X

end count = %X

```

```

Timer Error, expected the Limit Bit to be set

Address = %X

Data = %X

Interrupt table has incorrect value

expected = %4X

observed = %4X

Interrupt Pending Register has incorrect value

level = %d

expected = %4X

observed = %4X

User Timer mode not counting

start count = %X.%X

end count = %X.%X

```

# Subtest: BW Tag RAM 6N

• ID: 18.1 • Level: 8

• Attributes: Test Module

Initialization Module

Test the Bus Watcher Tag RAMs with a 6N algorithm.

The test is meant to be called by the POST sequencer. The code is meant to be run in diag mode only. The test is executed from the CPU's Icache.

- Determine BW tag size and mode configured.

- Execute the 6N test on the tags.

- First pass: write in ascending order.

- Second pass: read-then-write in ascending order.

- Third pass: read-compare in descending order.

- · Loop for all patterns.

# Possible Error Messages

```

Data Compare Error

address = %X

expected = %X

observed = %X

```

○○○● ●●●○ C0 MQH 0x1E

• ID: 30.0

• Attributes: General Purpose

• Diagnosis: MQH0

Set Configuration 0 and test the MQH.

Subtest: C\_0 BW, MQH

ID: 30.1 Level: 1

• Attributes: Error Terminates Sequencer

Error is Fatal

Establish the board configuration for this test.

Possible Error Messages

This module does not check or report errors.

Subtest: MQH Registers

ID: 30.2 Level: 8

Attributes: Test Module

**Error Terminates Sequencer**

Test the read and write accessibility of the MQH ASIC registers, using all access sizes allowed. The addresses of the MQH registers are in CSR space. If any access causes a data access exception or unexpected interrupt, the test aborts with a FAIL status.

The ECC Error registers are read only. Testing is limited to insuring that register access does not cause a trap and that all error bits are cleared.

The Group Type registers are read only; they are not tested.

To prevent losing refresh, the Refresh Enable bit in the MCSR is never reset.

When appropriate, the test restores the original value it found in the register.

```

While testing %s register an unexpected trap occurred

MFSR = %X

MFAR = %X

Trap Type = %2x

CC Error = %X.%X

Unexpected Component ID value

address = %X

expected = %X or %X

observed = %X

%s register failed to return correct data

address = %X

expected = %X

observed = %X

%s register failed to return correct data

expected = %X.%X

observed = %X.%X

Floating a bit through %s register failed

expected = %X

observed = %X

Floating a bit through %s register failed

expected = %X.%X

observed = %X.%X

```

# Subtest: MQH Initialization

• ID: 30.3 • Level: 1

• Attributes: Error is Fatal

Set up the MQH timing registers and control register. Timing values loaded depend on the types of SIMMs present. Turn on Refresh Enable, set Refresh Count, Request Delay.

# Possible Error Messages

This module does not check or report errors.

Subtest: Enable ECC

• ID: 30.4 • Level: 1

• Attributes: Error is Fatal

Enable ECC checking on the MQH.

Possible Error Messages

This module does not check or report errors.

# Subtest: Memory

• ID: 30.5 • Level: 8

Attributes: Test Module

Test all memory on this MQH. If a group with memory is not found, return FAIL. The purpose of the test is to test enough memory to allow the consistency tests to run. The memory test functions are loaded into the Icache for speed.